提供客戶的主要益處

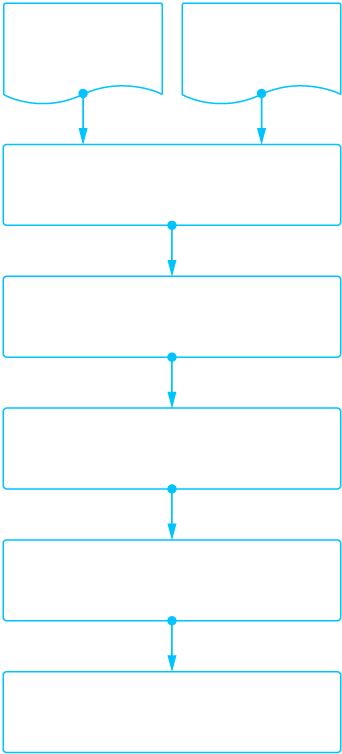

聯電的數位設計參考流程將任何有關設計單元資料庫,技術的問題減到最小或是完全排除。簡短來說,我們的參考設計流程大大的縮短了:

試產時程

上市時程

量產時程

為因應目前迴路設計公司所面臨深次微米設計的挑戰,聯電的數位設計參考流程提供客戶指導方針,透過使用標準邏輯閘元件庫及由各 IP 供應商提供之確認準據與各類技術檔案來完成電路設計。聯電的數位設計流程整合了電子設計自動化廠商的基線設計流程,來解決時序收斂,信號整合,耗電等問題。聯電的數位設計參考流程涵蓋了從 RTL 合成、Design-for-Test、 Place-and-Route、RC Extraction,靜態時序分析到 DRC / LVS 確認,並且支援 Cadence 以及 Synopsys 的電子設計自動化工具。

聯電的數位設計參考流程將任何有關設計單元資料庫,技術的問題減到最小或是完全排除。簡短來說,我們的參考設計流程大大的縮短了:

試產時程

上市時程

量產時程