Key Benefits to Customers

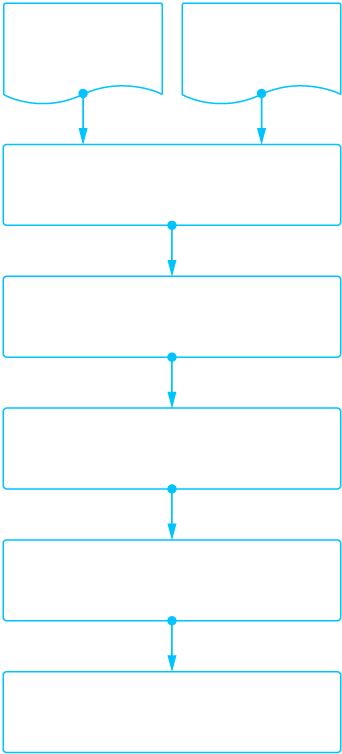

The UMC Digital Design Reference Flows minimize or eliminate any library, technology, tool and flow issues prior to customers' using the libraries and technology file during implementation. In brief, it significantly shortens :

Time to Tape out

Time to Market

Time to Volume